从 PLA 到 FPGA:可编程逻辑器件 40 年进化史

💡 想象你是一名 1980 年代的数字电路工程师。你接到一个任务:设计一块自定义逻辑电路,实现几十个信号的组合与时序控制。

你面前只有两条路:

- 路线 A:ASIC 定制芯片——性能极致,但设计周期半年起步,流片费用数十万美元,一旦出错全部报废

- 路线 B:74 系列通用芯片手搭——买一堆 74LS00、74LS138,在面包板上飞线连接,调试到怀疑人生

有没有第三条路?一种芯片,买回来就能编程,编错了还能擦掉重来?

这个问题,驱动了可编程逻辑器件(PLD)整整 40 年的进化——从最早的 PLA,到 PAL、GAL、CPLD,最终催生出今天的 FPGA。每一代的诞生,都是为了解决上一代的致命缺陷。

这篇文章会带你沿着这条进化链走一遍,重点回答一个核心问题:FPGA 为什么能成为最终的赢家?

目录

- 1. 为什么要了解这段历史

- 2. FPGA 的四代”前辈”

- 3. FPGA 的诞生:一次架构革命

- 4. FPGA vs CPLD:新王与旧王

- 5. FPGA 的未来:从芯片到平台

- 6. 总结

- 常见问题

- 参考资料

1. 为什么要了解这段历史

你可能会想:我直接学 FPGA 就好了,为什么要了解那些已经淘汰的老器件?

三个理由:

- 理解设计哲学——FPGA 的核心架构(LUT + 触发器 + 可编程互联)不是拍脑袋想出来的,而是从 PLA/PAL/CPLD 一步步”进化”来的。了解进化逻辑,你才能真正理解 FPGA 为什么长成今天这个样子

- 看懂技术选型——在一些对成本和功耗敏感的场景,CPLD 至今仍在使用。理解它和 FPGA 的本质差异,才能做出正确的选型决策

- 建立技术直觉——每一代器件的”进化跳跃”背后,都有一个工程问题驱动。这种”问题→方案→新问题→新方案”的思维模式,对你未来的工程生涯非常有价值

2. FPGA 的四代”前辈”

在 FPGA 登场之前,可编程逻辑器件(PLD, Programmable Logic Device)经历了四代进化。我们不需要深入每一代的电路细节——重要的是理解每一代解决了什么问题、又留下了什么遗憾。

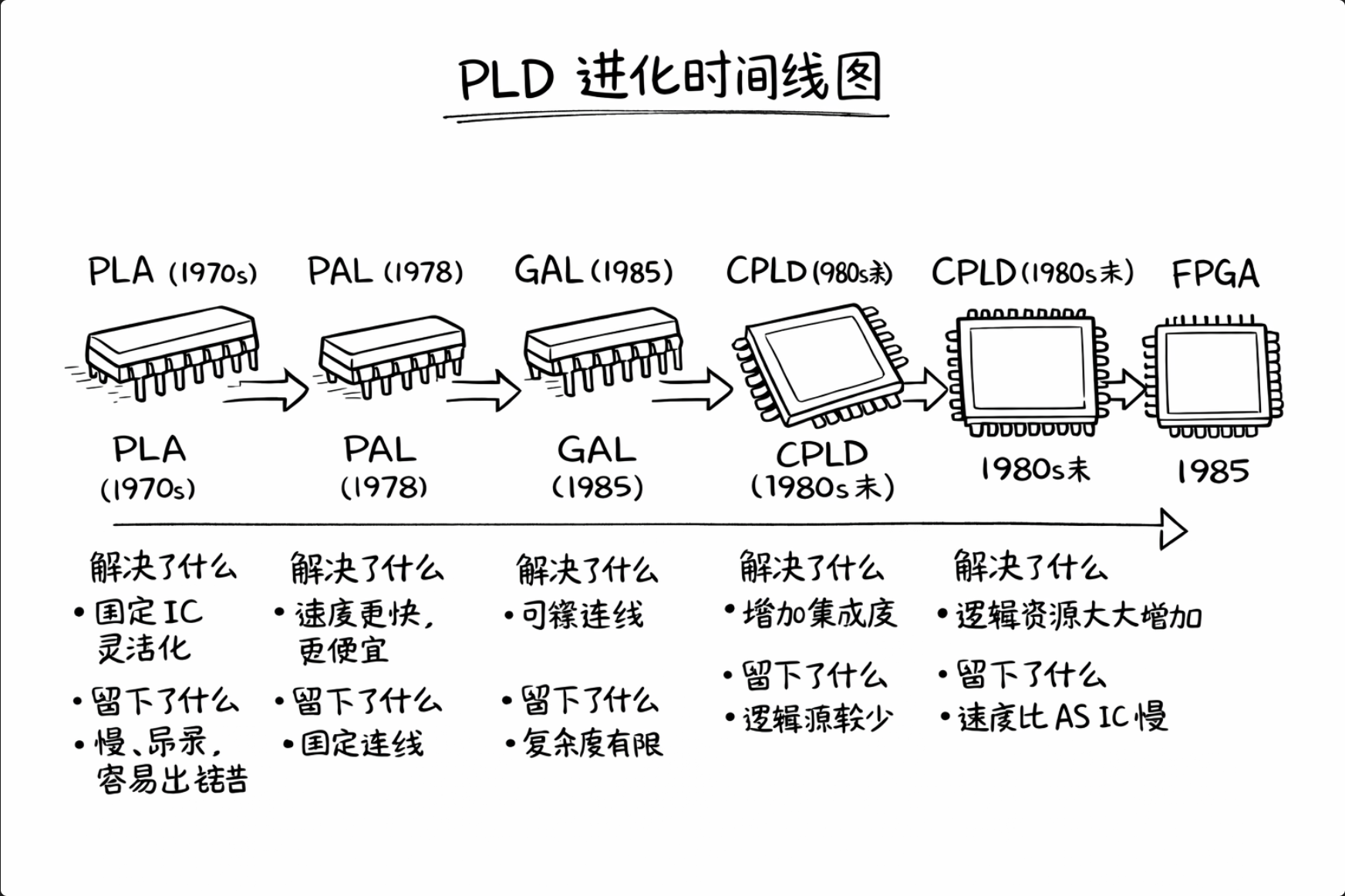

进化总览

| 世代 | 器件 | 年代 | 解决了什么问题 | 留下了什么遗憾 |

|---|---|---|---|---|

| 第1代 | PLA(可编程逻辑阵列) | 1970s | 首次实现”买回来就能编程”的逻辑芯片 | 结构复杂、速度慢、成本高 |

| 第2代 | PAL(可编程阵列逻辑) | 1978 | 简化结构、提升速度、降低成本 | 只能编程一次(熔丝工艺),输出结构固定 |

| 第3代 | GAL(通用阵列逻辑) | 1985 | 可重复编程(电可擦除),输出可配置 | 逻辑容量仍然很小(几百门) |

| 第4代 | CPLD(复杂可编程逻辑器件) | 1980s末 | 多个逻辑块互联,容量提升到中大规模 | 基于”与-或”阵列,扩展性有天花板 |

逐代速览

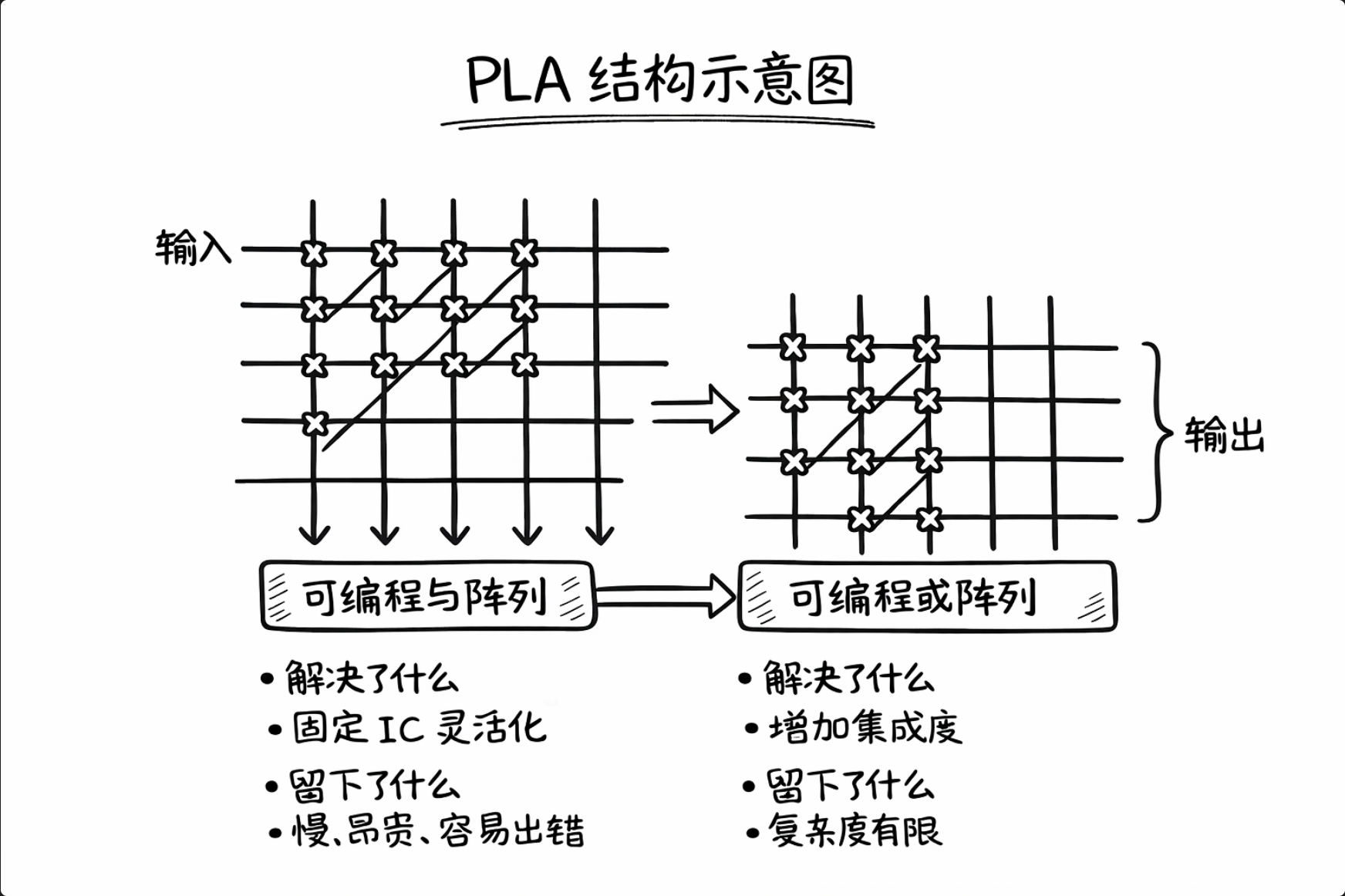

第 1 代:PLA——可编程逻辑的开山之作

PLA(Programmable Logic Array,可编程逻辑阵列)是最早的可编程逻辑器件,诞生于 1970 年代。它的核心思想非常朴素:用一个可编程的”与”阵列和一个可编程的”或”阵列来实现任意的 SOP(Sum of Products,积之和)表达式。

简单说:你可以把 PLA 理解成一个”可编程的真值表”——告诉它输入和输出的对应关系,它就能帮你实现对应的组合逻辑。

但 PLA 的问题也很明显:两个阵列都可编程意味着结构复杂、延迟大、成本高。在那个年代,它只能用于小规模的逻辑电路。

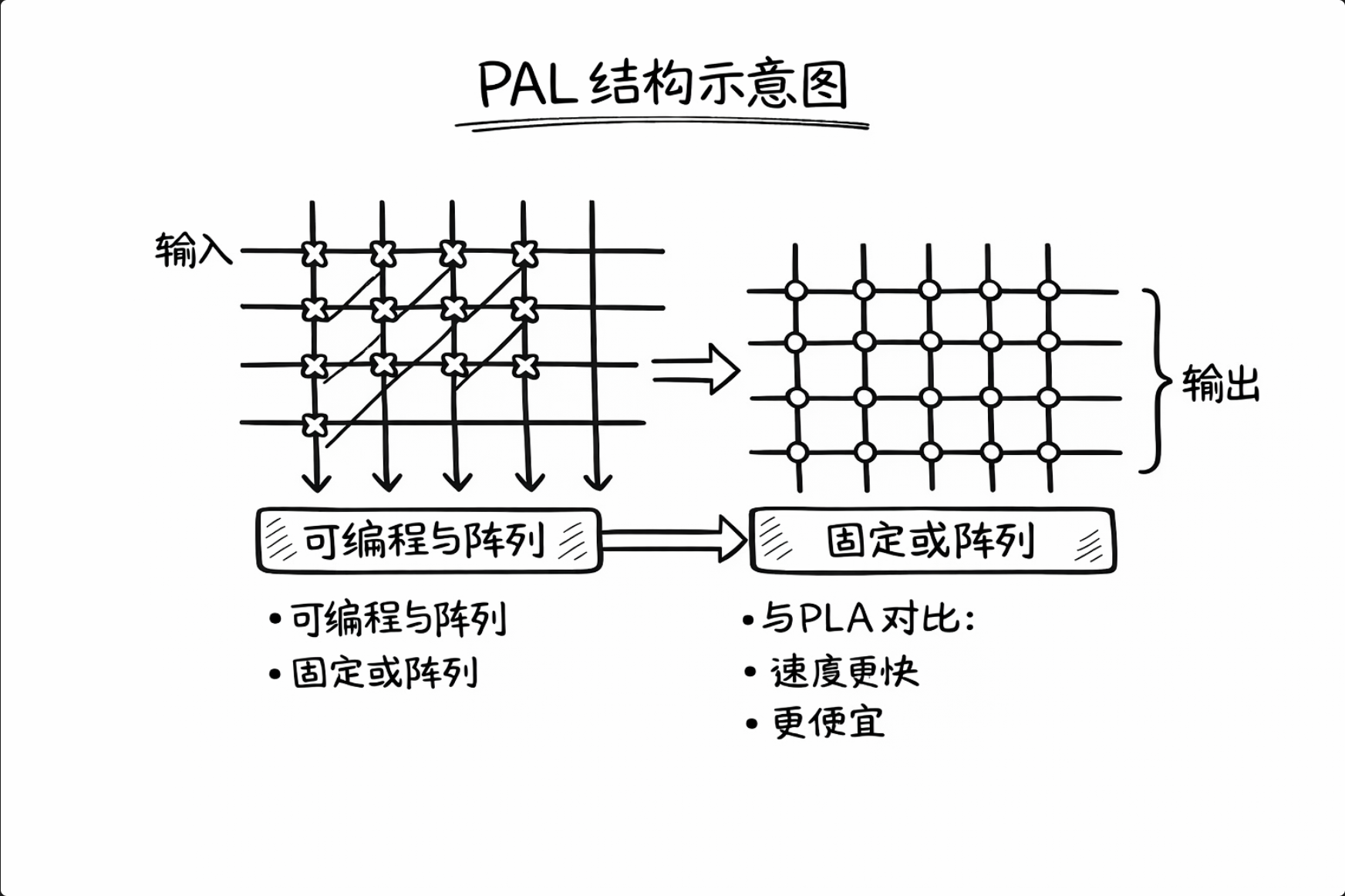

第 2 代:PAL——“砍掉一半复杂度”

PAL(Programmable Array Logic,可编程阵列逻辑)的改进思路非常直接:既然两个阵列都可编程太复杂了,那就只保留”与”阵列可编程,“或”阵列固定。

这一刀砍得很精准——结构简化了,速度提上去了,成本降下来了。PAL 迅速取代 PLA,成为 1980 年代最主流的可编程逻辑器件。

但 PAL 有一个致命缺陷:它采用熔丝工艺,编程时物理烧断连接——这意味着只能编程一次。烧错了?扔掉重来。

第 3 代:GAL——“终于可以重来了”

GAL(Generic Array Logic,通用阵列逻辑)解决了 PAL 的”一次性”问题。它采用电可擦除的 CMOS 工艺(E²CMOS),允许器件多次编程。同时,GAL 引入了输出逻辑宏单元(OLMC),让输出可以灵活配置为组合逻辑或寄存器输出。

这是一个重要的里程碑——“可重复编程”的特性第一次出现在可编程逻辑器件上。但 GAL 的逻辑容量仍然很小(几百门级别),只能做一些简单的”胶合逻辑”。

💡 工程师手记:如果你上过大学的数字电路实验课,可能用过 GAL16V8 或 GAL22V10——那就是 GAL 器件。当时我们用它做简单的地址译码和状态机,就已经能感受到”可编程”带来的便利了。不过说实话,GAL 能做的事情确实太有限了,稍微复杂一点的设计就塞不下。

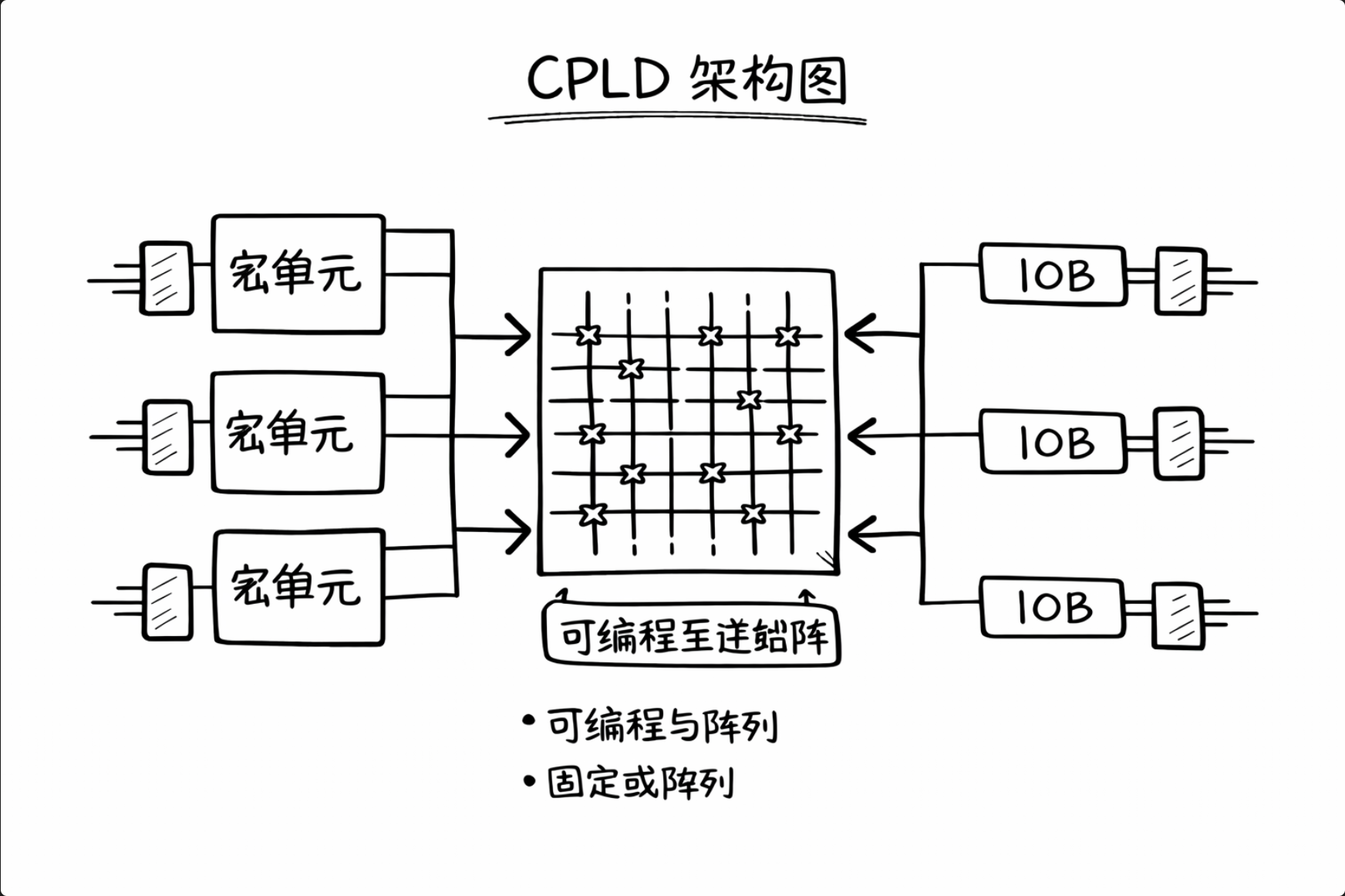

第 4 代:CPLD——“把小积木拼成大积木”

CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)的思路很巧妙:既然单个 PAL/GAL 容量不够,那就把多个小规模逻辑块(宏单元)通过可编程互连矩阵连接起来,形成一个中大规模的可编程逻辑器件。

CPLD 的每个宏单元本质上类似一个 PAL/GAL,包含逻辑门、触发器和可编程互连。外围是专用的 I/O 接口模块(IOB)。

CPLD 有两个显著优点:

- 时序可预测——互连结构相对简单,信号延迟固定,这对时序要求严格的设计非常友好

- 非易失性——基于 EEPROM/Flash 工艺,上电即可工作,不需要外部加载配置

但 CPLD 的扩展性有天花板。它的底层仍然是”与-或”阵列结构——当逻辑规模继续增大时,互连矩阵会变得极其复杂,布线资源消耗指数增长。

工程师们需要一种全新的架构来突破这个瓶颈。

3. FPGA 的诞生:一次架构革命

1985 年,Xilinx(赛灵思)推出了世界上第一颗 FPGA——XC2064。这颗芯片只有 64 个逻辑块、约 1000 个等效门——放到今天简直微不足道。但它开创了一种全新的架构范式,彻底改变了可编程逻辑的游戏规则。

关键跳跃:从”与-或阵列”到”查找表(LUT)”

这是 FPGA 与之前所有 PLD 器件最本质的区别,也是理解 FPGA 架构的核心:

- PLA/PAL/GAL/CPLD 的逻辑实现基于**“与-或”阵列**——本质上是实现 SOP 表达式。这种结构在逻辑规模小的时候很高效,但规模增大后互连复杂度急剧上升

- FPGA 的逻辑实现基于查找表(LUT, Look-Up Table)——本质上是一个小型的存储器。一个 N 输入的 LUT 可以实现任意的 N 输入组合逻辑,只需要把真值表存进去即可

💬 你可能会问:LUT 为什么更好?

想象你要实现一个 4 输入的组合逻辑。用”与-或”阵列,你需要根据具体的逻辑表达式来配置——不同的函数需要不同的连接方式,复杂度不可预测。

用 LUT 呢?不管你要实现什么函数,都只需要一个 16×1 的小存储器(2⁴ = 16 个存储单元)。把真值表写进去,完事。所有 4 输入逻辑函数的实现成本完全相同、延迟完全相同。

这意味着:LUT 架构的可预测性和扩展性远优于”与-或”阵列。这就是为什么 FPGA 能做到百万门级别,而 CPLD 在几万门就触及天花板。

FPGA 的内部架构

FPGA 的内部由三大核心组件构成:

1. CLB(可配置逻辑块)

CLB 是 FPGA 的基本逻辑单元,一个 CLB 通常包含:

- 若干个 LUT(查找表)——实现组合逻辑

- 若干个 FF(触发器)——实现时序逻辑

- 多路选择器——用于灵活配置数据通路

一颗 FPGA 芯片中往往有成千上万个 CLB,均匀地散布在芯片内部。

2. IOB(输入输出块)

环绕在 CLB 阵列的外围,负责 FPGA 与外部世界的信号交互。支持多种电气标准(LVDS、LVCMOS、HSTL 等)。

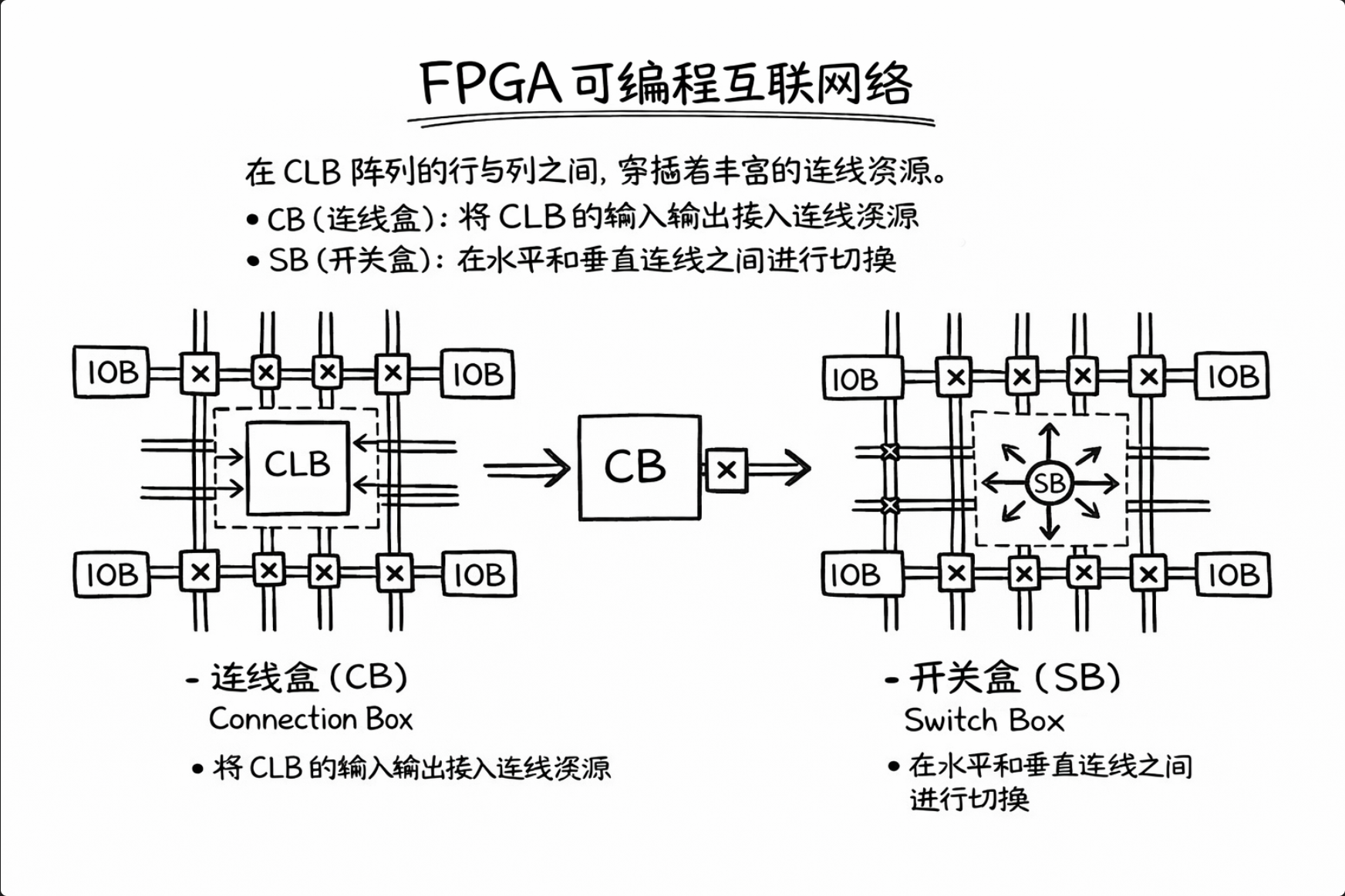

3. 可编程互联网络

这是 FPGA 架构中最关键也最复杂的部分。在 CLB 阵列的行与列之间,穿插着丰富的连线资源。为了实现灵活的连接,FPGA 引入了两种关键组件:

- 连线盒(CB, Connection Box)——将 CLB 的输入输出接入连线资源

- 开关盒(SB, Switch Box)——在水平和垂直连线之间进行切换

为什么 FPGA 用 SRAM 而不是 Flash?

与 CPLD 的非易失性存储不同,FPGA 通常采用基于 SRAM 的配置存储。这意味着:

- 优点:SRAM 可以无限次重写,而且制造工艺与标准逻辑工艺兼容,便于集成更多逻辑资源

- 代价:SRAM 是易失性的——每次上电,FPGA 需要从外部 Flash 加载配置数据(位流文件),才能开始工作

这是一个有意为之的工程权衡:牺牲了”上电即工作”的便利性,换来了更大的逻辑容量和更灵活的可重构性。

4. FPGA vs CPLD:新王与旧王

尽管 FPGA 在大多数场景中已经取代了 CPLD,但 CPLD 并没有完全消失。理解两者的本质差异,在实际选型时非常有用。

| 对比维度 | CPLD | FPGA |

|---|---|---|

| 逻辑实现 | ”与-或”阵列(乘积项) | 查找表(LUT) |

| 配置存储 | EEPROM/Flash(非易失性) | SRAM(易失性,需外部加载) |

| 上电行为 | 上电即工作 | 需从 Flash 加载位流(毫秒级) |

| 时序特性 | 延迟固定、可预测 | 延迟取决于布线,相对不确定 |

| 逻辑容量 | 几百~几万门 | 几万~数百万门 |

| 特殊资源 | 无 | Block RAM、DSP、SerDes、PLL 等 |

| 功耗 | 较低 | 较高(大规模设计时) |

| 典型应用 | 胶合逻辑、地址译码、小型状态机 | 信号处理、通信、AI 加速、ASIC 验证 |

💬 你可能会问:什么时候还会用 CPLD?

当你的设计满足以下条件时,CPLD 可能是更好的选择:

- 逻辑规模小(几百到几千门)

- 需要上电即工作(不能等加载时间)

- 对时序确定性要求极高

- 对成本和功耗敏感

典型场景:电源管理时序控制、简单的接口转换、PCB 上的”胶合逻辑”。

5. FPGA 的未来:从芯片到平台

FPGA 的进化并没有停止。从 1985 年的 XC2064(1000 门)到今天的 Versal(数百万门 + AI 引擎 + ARM 核),FPGA 已经从一颗”可编程逻辑芯片”进化成了一个异构计算平台。

三大趋势

1. 异构集成:FPGA + CPU + AI 引擎

现代 FPGA 不再是纯粹的可编程逻辑。Xilinx(现 AMD)的 Zynq 系列将 ARM 处理器核心与 FPGA 逻辑集成在同一颗芯片上;最新的 Versal 系列更进一步,集成了 AI 推理引擎(AIE)。Intel 的 Agilex 系列同样走上了异构集成的道路。

这意味着:未来的 FPGA 工程师不仅需要会写 Verilog,还需要理解软硬件协同设计。

2. AI 加速:FPGA 在数据中心的复兴

随着 AI 推理需求爆发,FPGA 凭借其可定制的计算流水线和灵活的精度配置(INT8、FP16 等),在数据中心和边缘计算领域获得了新生。微软的 Project Brainwave、AWS 的 F1 实例都大量使用了 FPGA。

3. 行业整合与中国力量

- 2015 年:Intel 以 167 亿美元收购 Altera

- 2022 年:AMD 以 350 亿美元收购 Xilinx

- 与此同时,国产 FPGA 厂商(紫光同创、安路科技、高云半导体、复旦微电子等)正在快速追赶,在中低端市场已经具备竞争力

💡 工程师手记:从行业趋势来看,FPGA 正在从”硬件工程师的专属工具”变成”系统架构师的标配技能”。如果你现在入行,建议不仅学传统的 RTL 设计,也要关注高层次综合(HLS)和软硬件协同开发——这是未来 FPGA 工程师的核心竞争力。

6. 总结

回顾可编程逻辑器件 40 年的进化,有一条清晰的主线:每一代都在解决上一代的致命缺陷。

| 世代 | 器件 | 关键突破 | 致命缺陷 |

|---|---|---|---|

| 第1代 | PLA | 首个可编程逻辑芯片 | 太复杂、太慢、太贵 |

| 第2代 | PAL | 简化结构,速度↑ 成本↓ | 只能编程一次 |

| 第3代 | GAL | 可重复编程 | 容量太小 |

| 第4代 | CPLD | 多块互联,容量↑ | “与-或”架构扩展性有限 |

| 第5代 | FPGA | LUT 架构 + SRAM 配置 | 开发复杂、单价高(但不断改善中) |

FPGA 之所以成为最终的赢家,核心在于那次从”与-或阵列”到”查找表”的架构跳跃——这让它突破了 CPLD 的规模天花板,拥有了从几千门扩展到数百万门的能力。

如果你正在学习 FPGA,理解这段进化史能帮你建立一个重要的直觉:技术发展不是随机的,每一个设计决策背后都有工程问题在驱动。带着这个思维方式,你会学得更深、更快。

常见问题

Q1:PLA/PAL/GAL 现在还有人用吗?

PLA 和 PAL 已经基本退出市场。GAL 在一些遗留系统(Legacy System)中还能见到,但新设计几乎不会采用。CPLD 仍然活跃在一些对成本、功耗和上电时间敏感的小规模应用中。

Q2:CPLD 和 FPGA 我该学哪个?

直接学 FPGA。FPGA 完全覆盖了 CPLD 的能力范围,而且市场需求远大于 CPLD。CPLD 的知识在你学会 FPGA 后自然就理解了——它本质上是 FPGA 的”简化前辈”。

Q3:为什么 FPGA 用 LUT 而不是继续用”与-或”阵列?

因为”与-或”阵列的互连复杂度随规模指数增长,扩展性有硬上限。而 LUT 架构将逻辑实现和互连解耦——每个 LUT 独立实现局部逻辑,再通过可编程互联网络连接。这种”分而治之”的策略让 FPGA 可以轻松扩展到百万门级别。

Q4:国产 FPGA 现在发展到什么程度了?

国产 FPGA 在中低端领域已经可以替代部分 Xilinx/Intel 产品,但在高端领域(28nm 以下工艺、大规模逻辑容量、高速 SerDes)仍有显著差距。代表厂商包括紫光同创(Pango)、安路科技(Anlogic)、高云半导体(Gowin)、复旦微电子等。如果你做的是非军工、非航天的中低端项目,国产 FPGA 值得关注。

参考资料

- Xilinx/AMD,UG474: 7 Series FPGAs Configurable Logic Block User Guide

- Stephen Brown & Zvonko Vranesic,Fundamentals of Digital Logic with Verilog Design

- 维基百科,Programmable Logic Device

- 维基百科,Field-Programmable Gate Array - History

系列导航:本文是「FPGA 入门系列」第 2 篇。

如果这篇文章对你有帮助,欢迎点赞、收藏,也欢迎在评论区聊聊你对 FPGA 历史的看法——技术交流才是最好的学习方式。