FPGA 是什么?一个嵌入式 FPGA 工程师的入门解读

💡 假设你接到一个任务:设计一个系统,要求同时采集 8 路 ADC 信号、实时做 FFT 变换、再通过以太网上传数据,整条链路延迟不超过 100 微秒。

用 STM32?单核算力扛不住 8 路并行。用 Linux + ARM?实时性不够,操作系统调度一抖就超时。用 ASIC?项目还在原型阶段,流片的钱比你年薪还高。

这时候就只剩一个选择了——FPGA。

FPGA 在数字电路领域是一个你绕不开的名字。它既不像 CPU 那样靠执行软件指令来完成任务,也不像 ASIC 那样一旦制造就无法更改。它更像一块数字世界的乐高积木——你可以反复”搭建”和”拆解”,组合出任意数字逻辑电路。

这篇文章会带你从零开始理解:FPGA 到底是什么、它内部长什么样、它和 CPU 的本质区别在哪里、以及什么时候你应该考虑用它。

目录

1. 什么是 FPGA

一句话定义

FPGA(Field-Programmable Gate Array,现场可编程门阵列) 是一种以数字逻辑为核心的集成芯片。你可以通过加载一个配置文件(称为位流文件 / Bitstream),让它变成你想要的任何数字电路。

这个名字本身就高度概括了它的核心特征,我们逐词拆解一下:

| 英文 | 含义 | 关键点 |

|---|---|---|

| Field | 现场 | 芯片出厂后,你可以在实验室、产线上随时编程,不需要返回芯片工厂 |

| Programmable | 可编程 | 功能不是固定的,可以反复修改、升级 |

| Gate | 门(逻辑门) | 最基础的数字逻辑单元——与门、或门、非门等 |

| Array | 阵列 | 大量逻辑单元按阵列排布,通过互联网络连接在一起 |

连起来就是:一块由大量逻辑门排列成阵列、你可以在现场反复编程的芯片。

用乐高来理解 FPGA

如果上面的定义还是太抽象,试试这个类比:

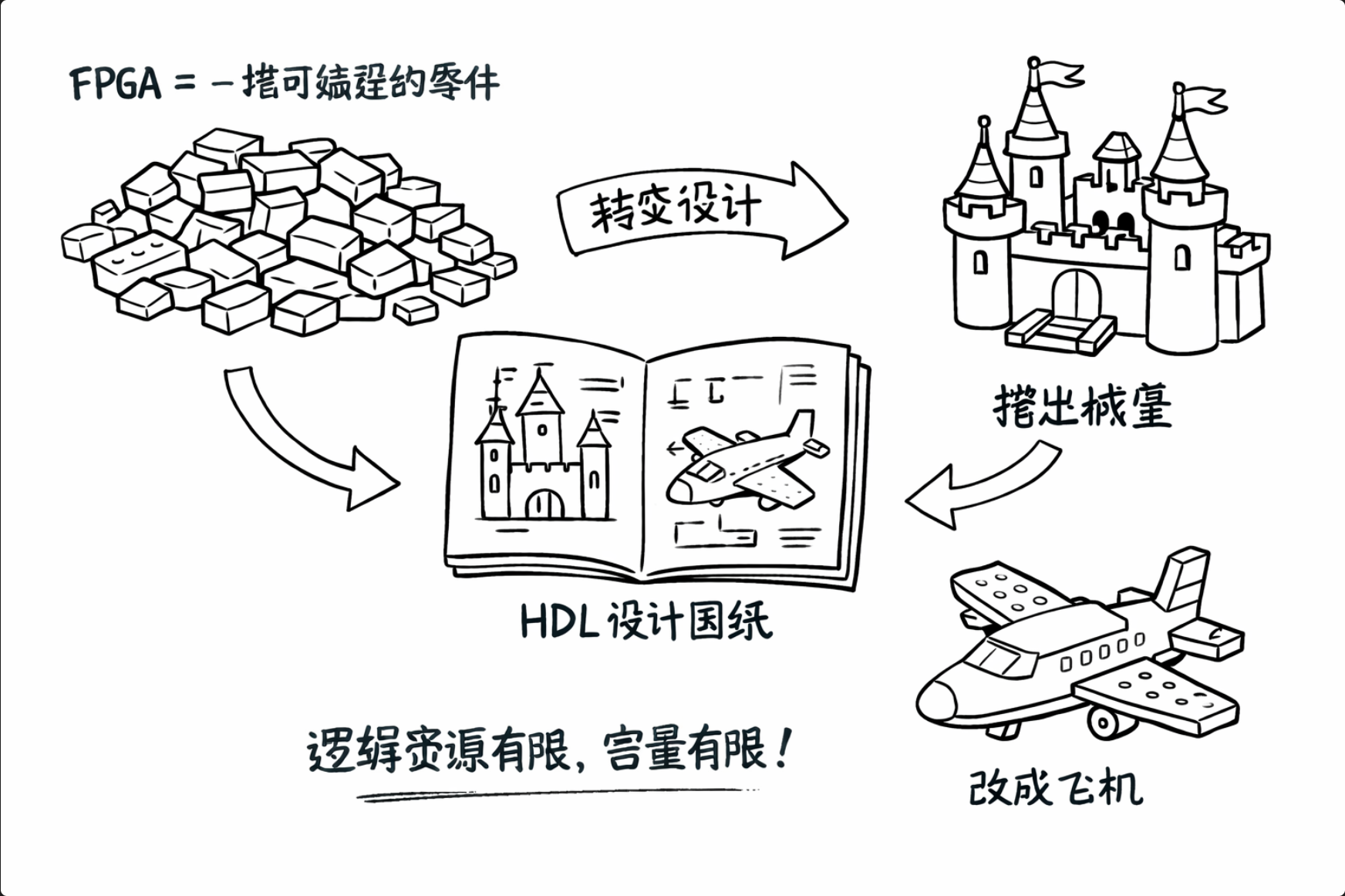

想象你买了一大盒乐高积木。打开盒子的时候,里面全是散装零件——这就是 FPGA 出厂时的状态:一堆可编程的逻辑资源等着被”拼装”。

你拿出一份图纸(用 HDL 硬件描述语言写的代码),按图纸把零件拼成了一座城堡(一个特定的数字电路)。用了一段时间,你想把城堡拆掉改成一架飞机——没问题,重新拼就行(重新编程 FPGA)。

唯一的限制是什么?零件的数量。你不可能用 100 块零件拼出一个需要 10000 块的作品。FPGA 也一样,逻辑资源是有限的,你的设计不能超出芯片的容量。

💡 工程师手记:我第一次真正”感受到” FPGA 的灵活性,是在学习用 FPGA 实现 UART 串口收发功能的时候。同一块开发板,我之前先烧了一个 8 位计数器驱动 LED,然后重新生成位流,又让它变成了一个 UART 串口收发器。芯片没换、板子没动、焊都没重新焊,但功能完全不一样了。那种感觉就像手里握着一块橡皮泥——你想捏成什么就捏成什么。

FPGA 的历史定位

FPGA 并不是凭空出现的。在它诞生之前,工程师如果想实现数字逻辑,只有两条路:

- ASIC(专用集成电路):性能极致,但一旦流片就无法修改,设计周期长、试错成本极高

- 早期可编程器件(PLA / PAL / CPLD):可以编程,但逻辑容量太小(几百到几千门),只能做简单的”胶合逻辑”

1985 年,Xilinx 推出了第一颗 FPGA——XC2064,开创了”现场可编程”的先河。FPGA 作为一种半定制电路,同时解决了上述两个痛点:它比 ASIC 灵活(可以反复重编程),又比早期可编程器件强大得多(逻辑容量大了几个数量级)。

2. FPGA 内部有什么

FPGA 之所以能实现如此灵活的功能,是因为它内部集成了丰富的可编程资源。你可以把 FPGA 想象成一座城市——逻辑块是建筑物,互联线路是道路网,I/O 块是城市的出入口。

下面是 FPGA 内部的核心资源:

| 资源 | 全称 | 它是做什么的 |

|---|---|---|

| CLB | Configurable Logic Block(可配置逻辑块) | FPGA 的”大脑”——包含查找表(LUT)和触发器(FF),用来实现组合逻辑和时序逻辑 |

| IOB | I/O Block(输入输出块) | FPGA 与外部世界的”接口”——负责信号的输入输出,支持多种电气标准(LVDS、LVCMOS 等) |

| 互联网络 | Programmable Interconnect(可编程互联) | 连接所有资源的”高速公路网”——决定信号如何在芯片内部流动 |

| Block RAM | Block Random Access Memory(块存储器) | 片上存储——用于数据缓存、FIFO 等,无需外挂存储芯片即可高速存取 |

| DSP | Digital Signal Processing(数字信号处理单元) | 内置硬核乘法器和累加器——专门优化了乘加运算,广泛用于滤波、FFT 等 |

| PLL/MMCM | Phase-Locked Loop / Mixed-Mode Clock Manager | 时钟管理——用于时钟的倍频、分频、移相,为设计提供精确稳定的时钟 |

| SerDes | Serializer/Deserializer(高速串行收发器) | 高速通信接口——支持 Gbps 级别的串行通信,如 PCIe、以太网、HDMI 等 |

所有这些资源的连接关系和功能,都是通过加载位流文件(Bitstream) 来配置的——就像给乐高积木提供了一份精确的拼装图纸。

💬 你可能会问:FPGA 编程用什么语言?跟 C 语言有什么关系?

FPGA 不是用 C / Python 这类”编程语言”开发的,而是用硬件描述语言(HDL, Hardware Description Language),最常用的是 Verilog 和 VHDL。HDL 描述的不是”程序执行流程”,而是”硬件电路结构”——你写的每一行代码,都对应着芯片里的一段真实电路。这是 FPGA 开发和软件开发最本质的区别。

3. FPGA vs CPU:两种截然不同的计算哲学

这是理解 FPGA 最关键的一节。如果你只记住这篇文章的一个知识点,就记住这个:

CPU 是”执行指令的机器”,FPGA 是”你自己画的电路”。

CPU:按菜谱做菜的大厨

CPU 采用经典的冯·诺依曼架构,核心思想是:

- 程序指令和数据统一存储在内存中

- CPU 按照”取指令 → 译码 → 执行 → 写回”的流水线,逐条处理指令

- 数据通路、指令集、寄存器数量在制造时就已经固定——你只能在这个框架内写软件,不能改硬件本身

你可以把单核 CPU 想象成一个厨艺精湛的大厨:他有一本菜谱(指令集),严格按照菜谱的步骤一步步执行。他做菜速度很快,但同一时间只能做一道菜。想做更多菜?那就排队等。

CPU 的强项在于通用性:同一颗 CPU 可以运行操作系统、浏览器、游戏、编译器……但代价是,每个任务都必须排队通过”取指-执行”的流水线,无法跳出这个框架。

FPGA:100 个灶台同时开火的厨房

FPGA 的架构与 CPU 截然不同:

- 没有固定的指令集——你自己定义数据通路和处理逻辑

- 没有”取指-执行”的概念——逻辑功能直接由硬件门电路实现

- 核心架构由三大要素构成:

- 查找表(LUT):实现任意组合逻辑(相当于一个可编程的真值表)

- 触发器(FF):存储中间状态(一位数据的寄存器)

- 可编程互联:决定信号如何在各模块之间流转

如果说 CPU 是一个大厨在一个灶台上按菜谱做菜,那 FPGA 就是一个拥有 100 个灶台的厨房,100 道菜可以同时开火。每个灶台(逻辑单元)都独立工作、互不干扰。

一张表看清本质区别

| 对比维度 | CPU | FPGA |

|---|---|---|

| 工作方式 | 逐条读取指令 → 执行 | 所有逻辑电路同时运行 |

| 改变功能 | 换一套软件程序 | 重新加载位流文件(硬件重新配置) |

| 并行能力 | 有限(受核心数和线程数限制) | 真正的硬件级并行,每个逻辑单元独立工作 |

| 延迟 | 受流水线、缓存、中断影响,延迟不确定 | 硬件直连,延迟确定且极低(纳秒级) |

| 擅长什么 | 复杂控制流、多任务调度、运行操作系统 | 大规模并行数据处理、硬实时控制、硬件加速 |

💡 工程师手记:我对这个差距感受最深的一次,是在做以太网数据包解析的时候。同样的功能,我分别用 C 语言(跑在 ARM Cortex-A9 上)和 Verilog(跑在 FPGA 上)实现过。ARM 版本需要中断响应、内存拷贝、协议栈逐层解析,处理一个包需要几十微秒;FPGA 版本直接用流水线逐字节解析,从第一个字节到达到解析结果输出,只需要几个时钟周期——不到 100 纳秒。差了三个数量级。

那一刻我才真正理解:CPU 是”执行指令来模拟功能”,FPGA 是”电路本身就是功能”。

4. FPGA 的优势与代价

任何技术都有它的适用边界。只讲优势不讲代价,不是客观的技术分享。

四大优势

1. 灵活可重构

FPGA 可以随时重新编程:修改设计、修复 Bug、升级功能,只需重新生成并加载位流文件,无需更换硬件。在 5G 基站中,FPGA 可以通过远程更新位流来支持新的通信协议版本——硬件不动,功能升级。

2. 真正的硬件并行

FPGA 的每一个逻辑单元都可以独立、同时地工作。你可以同时运行几十甚至上百个处理模块,互不干扰。这不是软件里”开多线程”的那种并行——那只是操作系统在时间片之间快速切换制造的幻觉。FPGA 的并行是物理层面同时发生的。

💡 工程师手记:有一次我需要同时做 4 路视频流的图像缩放。用 ARM + DMA 的方案折腾了一周还是会丢帧;换成 FPGA 后,4 路缩放模块完全独立并行运行,每路都稳稳的不丢帧。那一刻我才真正体会到”真并行”和”假并行”的差距。

3. 高性能低延迟

逻辑功能由硬件门电路直接实现,没有取指令、译码、执行的流水线开销。信号从输入到输出的延迟可以做到纳秒级,特别适合高频交易、实时控制、高速通信等对延迟极其敏感的场景。

4. I/O 灵活性

FPGA 提供大量可配置的 I/O 引脚(从几十到上千个),每个引脚的电气标准(LVDS、LVCMOS、HSTL 等)、驱动能力、上下拉都可以独立配置。在系统集成中,FPGA 经常被用作”万能协议转换器”,把不同接口标准的设备无缝连接在一起。

三大代价

1. 开发周期长、学习曲线陡

用 C 语言实现一个功能可能写 50 行代码,用 Verilog 可能需要 500 行——而且还要关心时序约束、资源利用率、布局布线。FPGA 开发不是”写代码”,而是”设计电路”,思维方式完全不同。对于习惯了软件开发的人来说,这是一道不小的门槛。

2. 单价较高

同等算力下,FPGA 的单片价格远高于 MCU 或通用处理器。一颗中端 FPGA 的价格可能是一颗 STM32 的几十倍。因此 FPGA 更适合中小批量或原型验证场景,百万级量产通常会转向 ASIC。

3. 主频和能效不如专用芯片

FPGA 的可编程性是有代价的——同等功能下,FPGA 的面积、功耗、最高主频都不如专门为该功能设计的 ASIC。FPGA 主频通常在几百 MHz 级别,而 CPU 轻松上 GHz,ASIC 可以更高。

💬 你可能会问:FPGA 既然有这些缺点,为什么没被淘汰?

因为在很多场景下,FPGA 的优势远大于代价。当你需要”硬件级性能 + 软件级灵活性”的时候,FPGA 就是那个中间地带的唯一解。它不是最快的,也不是最便宜的,但它是最灵活的硬件方案。

5. 什么时候该用 FPGA

横向对比:五大计算平台

在选择芯片方案之前,先快速了解五大计算平台各自的定位:

| 平台 | 一句话定位 | 延迟 | 灵活性 | 量产成本 |

|---|---|---|---|---|

| MCU | 低成本嵌入式控制器 | 微秒级 | 高(改软件) | 极低 |

| CPU | 通用计算处理器 | 微秒~毫秒级 | 高(改软件) | 中 |

| GPU | 大规模数据并行(AI训练/图形渲染) | 毫秒级 | 中(改算法) | 中~高 |

| FPGA | 可重构硬件加速平台 | 纳秒~微秒级 | 高(改硬件逻辑) | 较高 |

| ASIC | 固定功能专用芯片 | 纳秒级 | 极低(不可更改) | 量产后极低 |

选型经验法则

- 需要跑操作系统、复杂业务逻辑 → 选 CPU

- 需要大规模并行训练(AI / 图形渲染) → 选 GPU

- 需要低成本嵌入式控制 → 选 MCU

- 需要百万级量产、功能完全固定 → 选 ASIC

- 需要灵活可变 + 硬件级加速 + 中小批量 + 原型验证 → 选 FPGA

FPGA 的典型应用领域

| 领域 | 典型应用 | 为什么选 FPGA |

|---|---|---|

| 通信 | 5G 基站、以太网交换、光纤通信 | 高带宽、低延迟、协议可灵活升级 |

| 图像/视频 | ISP 图像处理、视频编解码、医学影像 | 实时并行流水线,帧率有保证 |

| 信号处理 | 雷达、软件无线电(SDR)、FFT/FIR 滤波 | 内置 DSP 硬核,海量并行乘加运算 |

| 工业控制 | 电机驱动、机器人运动控制 | 精确时序控制,微秒级响应 |

| ASIC 验证 | SoC 流片前功能验证 | 接近真实硬件的验证环境,降低流片风险 |

| 数据中心 | AI 推理加速、数据压缩、加密解密 | 可定制计算流水线,能效比优于通用处理器 |

6. 总结

通过这篇文章,我们建立了关于 FPGA 的几个核心认知:

| 要点 | 核心内容 |

|---|---|

| FPGA 是什么 | 现场可编程门阵列——一种可以反复配置的数字逻辑芯片 |

| 内部有什么 | CLB(逻辑)、IOB(I/O)、互联网络、Block RAM(存储)、DSP(乘加)、PLL(时钟)、SerDes(高速通信) |

| vs CPU 的本质区别 | CPU 是”逐条执行指令的机器”,FPGA 是”你自己画出来的电路” |

| 优势 | 灵活可重构、真正硬件并行、纳秒级低延迟、I/O 灵活 |

| 代价 | 开发周期长、学习曲线陡、单价高、主频和能效不如 ASIC |

| 什么时候用 | 需要硬件级性能 + 灵活可变 + 中小批量 → FPGA 是最佳选择 |

FPGA 是通往数字电路设计世界的一把钥匙。如果你正打算入门,建议接下来继续了解 FPGA 的内部架构细节 和 开发流程,从”理解概念”迈向”动手实践”。

常见问题

Q1:FPGA 编程难吗?需要什么基础?

FPGA 开发的学习曲线确实比软件开发陡一些。你需要掌握:数字电路基础(组合逻辑、时序逻辑)、至少一种 HDL 语言(推荐 Verilog 入门)、以及 FPGA 开发工具的基本使用(如 Vivado 或 Quartus)。如果你有数字电路课程的基础,入门会顺畅很多。

Q2:学 FPGA 需要买开发板吗?用什么软件?

建议买一块入门开发板来配合学习——纯仿真虽然也能学,但上板实操能让你对”时序”和”资源”有更直观的体感。入门板推荐 Xilinx 或 Intel(Altera)系列,价格从几十到几百元不等。开发软件方面,Xilinx 用 Vivado,Intel 用 Quartus Prime,两者都有免费版本。

Q3:FPGA 那么好,为什么没有取代 CPU?

因为 FPGA 的灵活是有代价的。FPGA 开发效率远低于软件开发(实现同一功能,Verilog 的代码量和调试时间可能是 C 语言的 10 倍),而且 FPGA 不擅长复杂的控制流和多任务调度——这正是 CPU 的强项。FPGA 是在特定场景下的最优解,不是通用的万能解。

Q4:Verilog 和 VHDL 选哪个?

国内业界以 Verilog 为主流(语法更接近 C,上手更快),欧洲和航空航天领域 VHDL 更常见。如果你没有特殊要求,推荐从 Verilog 开始。

参考资料

- Xilinx/AMD,UG474: 7 Series FPGAs Configurable Logic Block User Guide

- Intel/Altera,AN 307: Altera Design Flow for Xilinx Users

- Steve Kilts,Advanced FPGA Design: Architecture, Implementation, and Optimization(《FPGA 高级数字设计》)

- 维基百科,Field-Programmable Gate Array

系列导航:本文是「FPGA 入门系列」第 1 篇。下一篇:FPGA 发展历程

如果这篇文章对你有帮助,欢迎点赞、收藏,也欢迎在评论区分享你对 FPGA 的理解或疑问——技术交流才是最好的学习方式。