数字电路中的竞争和冒险

1. 什么是竞争

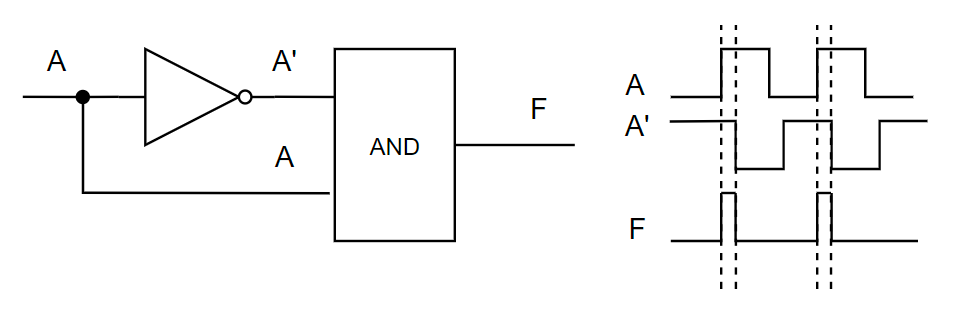

竞争(Race Condition)是指在组合逻辑电路中,当多个输入信号同时变化时,由于路径延迟不同,导致信号到达逻辑门的先后顺序不确定,从而使电路输出结果产生不确定的现象。如下图所示:

2. 什么是冒险

冒险(Hazard)冒险是指由于门电路延迟的存在,在输入信号变化过程中,输出端可能出现瞬时的错误尖峰脉冲(毛刺)的现象。即使最终输出正确,中间过程也可能出错。

- 类型:

- 静态冒险(Static Hazard):输出应保持不变(0或1),但出现了瞬时的相反电平脉冲

- 静态0冒险:输出应保持0,但出现1的尖峰。

- 静态1冒险:输出应保持1,但出现0的尖峰。

- 动态冒险(Dynamic Hazard):输出在从0变1(或1变0)的过程中,出现多次跳变。

- 功能冒险(Functional Hazard):由于多个输入同时变化,导致的逻辑功能问题。

- 静态冒险(Static Hazard):输出应保持不变(0或1),但出现了瞬时的相反电平脉冲

- 影响:在高速电路中,可能导致后续级联电路错误触发,或在时序电路中引起错误状态转换。例如,在一个XOR门电路中,如果输入A和B同时变化,输出可能出现毛刺。

3. 竞争和冒险的产生原因

竞争和冒险在数字电路设计中很常见,尤其在异步设计或时序不严格的电路中。如果不处理,可能导致芯片功能失效或可靠性降低。竞争和冒险的产生原因主要有以下几点:

- 组合逻辑路径延迟不同:信号通过不同的逻辑门路径,到达同一节点的时间不同

- 不完善的逻辑设计:卡诺图化简时遗漏了必要的冗余项

- 信号多次通过同一变量:一个信号的变化通过不同路径到达同一逻辑门的不同输入端

4. 在Verilog描述硬件电路时如何避免竞争和冒险

在Verilog中,避免竞争和冒险的关键是采用同步设计原则、正确使用赋值语句,并优化逻辑结构。以下是具体方法:

4.1 避免竞争(Race Condition)的策略

-

使用非阻塞赋值(<=)代替阻塞赋值(=)

- 在always块中描述时序逻辑时,始终使用非阻塞赋值(<=)。这模拟了硬件的并行更新,避免模拟器中赋值的顺序依赖。

- 示例:

// ❌错误方式,使用阻塞赋值,可能导致竞争 always @(posedge clk) begin a = b; // 阻塞赋值,先更新a b = a; // 然后更新b,可能导致a和b的值交换不确定 end // ✅正确方式(使用非阻塞赋值): always @(posedge clk) begin a <= b; // 非阻塞,所有赋值在块结束时并行更新 b <= a; // 避免顺序依赖,模拟硬件行为 end- 原理:非阻塞赋值在always块结束时同时生效,类似于硬件寄存器的并行翻转。

-

采用同步设计:

- 所有的数据都在时钟的有效边沿(通常是上升沿)被采样并存入触发器(Flip-Flop)。在两个时钟沿之间,组合逻辑有充足的时间去稳定下来。即使组合逻辑在中间产生了毛刺(冒险),只要在下一个时钟沿到来之前毛刺已经消失,那么触发器就不会采样到这个错误的毛刺,从而保证了系统的稳定性。

- 使用同步复位代替异步复位,以减少亚稳态(metastable)风险。

- 示例:

// ❌ 错误示例:组合逻辑产生控制信号,易产生毛刺 module bad_design( input wire clk, input wire a, input wire b, output reg out ); wire temp; assign temp = (a & b) | (~a & ~b); // 组合逻辑可 能产生毛刺 always @(posedge clk) begin if (temp) // 如果temp有毛刺,可能导致错误采样 out <= 1'b1; else out <= 1'b0; end endmodule // ✅ 正确示例:将组合逻辑同步到时钟域 module good_design( input wire clk, input wire rst, input wire a, input wire b, output reg out ); reg a_r, b_r; // 输入寄存器 // 输入信号打拍同步 always @(posedge clk) begin if (rst) begin a_r <= 1'b0; b_r <= 1'b0; end else begin a_r <= a; b_r <= b; end end // 同步逻辑输出 always @(posedge clk) begin if (rst) out <= 1'b0; else out <= (a_r & b_r) | (~a_r & ~b_r); end endmodule -

避免产生组合逻辑环路:

- 示例:

// ❌ 错误示例:组合逻辑环路 module combinational_loop( input wire a, input wire b, output wire y ); wire temp; assign temp = a & y; // y依赖temp,temp依赖 y,形成环路 assign y = temp | b; // 竞争冒险 endmodule // ✅ 正确示例:打破环路,使用寄存器 module no_loop( input wire clk, input wire rst, input wire a, input wire b, output reg y ); always @(posedge clk) begin if (rst) y <= 1'b0; else y <= (a & y) | b; // 使用y的旧值,打破环路 end endmodule

4.2 避免冒险(Hazard)的策略

-

优化组合逻辑:

- 使用卡诺图(Karnaugh Map)或Quine-McCluskey方法简化逻辑表达式,确保覆盖所有可能输入变化,避免冗余项导致的冒险。

- 添加冗余逻辑以消除静态冒险。例如,对于一个有静态-1冒险的电路,添加额外项覆盖延迟路径。

- 示例:假设一个组合逻辑输出Y = A’B + BC(可能有冒险),添加冗余项A’C变成Y = A’B + BC + A’C,即可消除。

-

在Verilog中描述时,使用连续赋值或门级建模

- 对于组合逻辑,使用assign语句或always@(*)块,确保逻辑完整。

- 示例(潜在冒险电路):

assign y = (a & ~b) | (b & c); // 可能有静态冒险- 优化后:

assign y = (a & ~b) | (b & c) | (a & c); // 添加冗余项消除冒险

- 对于组合逻辑,使用assign语句或always@(*)块,确保逻辑完整。

-

插入寄存器或流水线:

- 在组合逻辑路径较长时,插入寄存器(pipeline)分解路径,减少延迟差异导致的冒险。这在时序电路中特别有效。

-

使用时钟门控或enable信号:

- 确保输入变化不会同时发生,或使用enable控制信号变化时机。

-

工具辅助验证:

- 在综合工具(如Vivado或Quartus)中使用时序分析(Timing Analysis)检测潜在冒险。

- 在模拟工具(如ModelSim)中运行门级仿真(post-synthesis simulation),添加延迟模型检查glitch。

4.3 总体设计原则

- 全同步设计:所有逻辑都在时钟边沿触发,避免异步组合逻辑直接控制关键信号

- 输入打拍:外部异步输入信号先打拍同步到时钟域

- 输出寄存:关键输出信号通过寄存器输出,消除组合逻辑毛刺

- 单一时钟:尽量使用单一时钟域,必要时使用标准的跨时钟域处理技术

- 完整覆盖:组合逻辑所有分支都要赋值,使用default和默认赋值

- 赋值规则:时序逻辑用非阻塞赋值(<=),组合逻辑用阻塞赋值(=)

- RTL级最佳实践:在Verilog RTL代码中,分离组合逻辑(always@(*))和时序逻辑(always@(posedge clk)),便于优化。

- 测试与验证:编写全面的testbench,覆盖角案例(corner cases),如同时输入变化。使用assertion检查不确定行为。

- 硬件考虑:在FPGA/ASIC实现时,关注布线延迟,使用约束文件(SDC)指定时序要求。

通过这些方法,可以显著降低竞争和冒险的风险,确保Verilog描述的电路在模拟和实际硬件中一致可靠。