FPGA FPGA开发流程

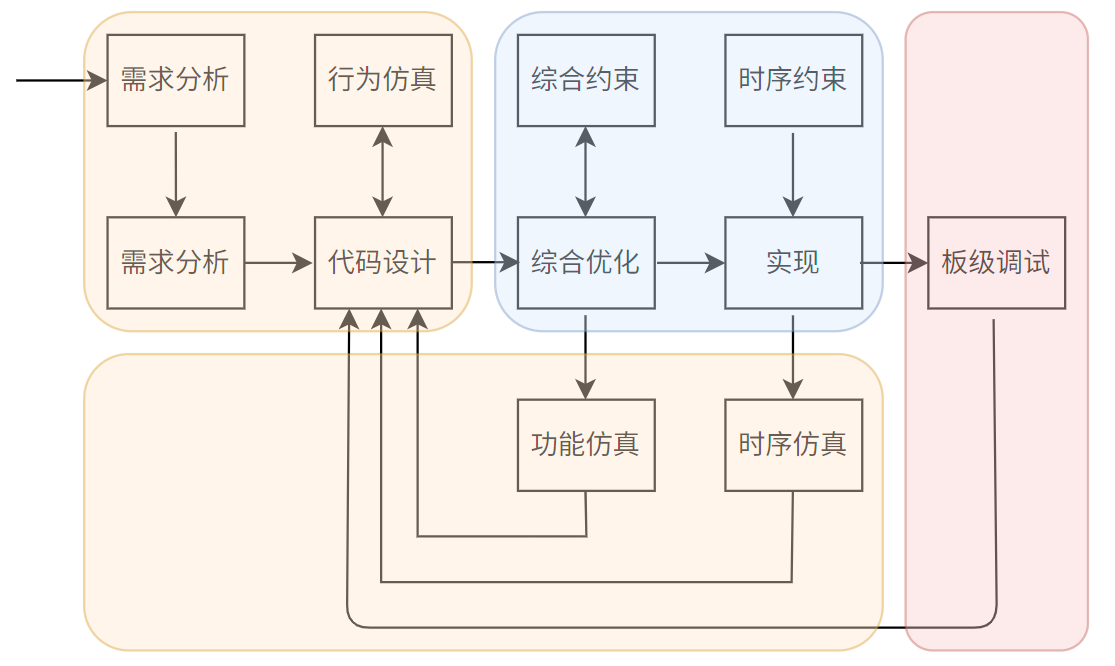

FPGA 开发流程可以分为三大阶段:设计输入与仿真、综合与实现、下载与调试。如下图所示:

1. 需求分析与规格定义(Requirements Analysis and Specification)

- 目的:明确项目目标,避免后期返工。

- 具体步骤:

- 收集用户需求:功能描述、性能指标(如时钟频率、延迟)、接口标准(e.g., PCIe、UART)、功耗预算、资源限制(LUT、FF、DSP 等)。

- 定义系统架构:划分模块(如控制逻辑、数据处理、I/O 接口),绘制高层框图。

- 选择 FPGA 芯片:根据需求选型(如 Xilinx Kintex 系列或 Intel Cyclone 系列),考虑容量、速度和成本。

- 工具/方法:使用文档工具如 Word 或 Visio 绘制框图;参考数据手册(Datasheet)。

- 注意:这一步是基础,如果规格不清晰,后续设计会反复修改。

- 类比:这是“建筑设计”阶段。需要和客户(或你自己)明确,要盖的是一栋办公楼还是一座公寓?几层楼高?有多少个房间?水电接口在哪里?

2. RTL 设计与编码(RTL Design and Coding)

- 目的:用硬件描述语言(HDL)实现逻辑功能。

- 具体步骤:

- 编写 RTL 代码:使用 Verilog、SystemVerilog 或 VHDL 描述电路行为。模块化设计,便于复用。

- 示例:定义状态机、组合逻辑、时序逻辑。避免非同步设计(如无时钟的锁存器)。

- 遵循编码规范:如可综合性(Synthesizable)代码,避免模拟专用语句。

- 工具/方法:编辑器如 VS Code、Vivado HLS(高层次综合,用于 C/C++ 转 RTL)。

- 注意:RTL 代表 Register Transfer Level,关注寄存器间的数据流动。

- 类比:这是“绘制施工图”阶段。用专业的语言(Verilog/VHDL)画出详细的电路结构图纸。对于复杂的模块(如电梯系统),直接采购一个成熟的IP核(电梯系统),然后设计接口把它装进你的大楼。

3. 功能仿真与验证(Functional Simulation and Verification)

- 目的:在软件环境中验证逻辑正确性,无需硬件。

- 具体步骤:

- 编写测试台(Testbench):模拟输入激励,检查输出。

- 运行仿真:检查波形、覆盖率(Code Coverage)。

- 类型:行为级仿真(快速验证)、门级仿真(更精确,但慢)。

- 工具/方法:ModelSim、Vivado Simulator、Verilator(开源)。

- 注意:发现 bug 后返回编码阶段。目标是 100% 功能覆盖。

- 类比:在正式施工前,在电脑上进行“3D建模和模拟”。模拟各种情况,比如刮风、下雨、人流进出,看看设计的结构是否合理、通道是否通畅。

4. 逻辑综合(Synthesis)

- 目的:将 RTL 代码转换为 FPGA 的逻辑门网表(Netlist)。

- 具体步骤:

- 运行综合工具:优化逻辑,映射到 FPGA 资源(如 LUT、FF)。

- 检查报告:资源利用率、初步时序估计。

- 约束定义:添加时钟约束、I/O 引脚分配(使用 .xdc 或 .qsf 文件)。

- 工具/方法:Vivado Synthesis、Quartus Synthesis。

- 注意:如果资源超标或时序不满足,需优化 RTL(如流水线)。

- 类比:这是“施工图纸”变成“施工方案”的过程。根据施工图纸,制定详细的施工方案,包括施工顺序、施工方法、施工材料等。施工队拿到图纸后,开始分析需要多少砖头(LUT)、多少钢筋(Flip-Flop)、多少预制板(RAM),并把它们组合成一个个标准的房间模块(网表)。

5. 实现与布局布线(Implementation: Place and Route)

- 目的:将网表物理映射到 FPGA 芯片上。

- 具体步骤:

- 布局(Placement):分配逻辑单元位置。决定网表中的每一个逻辑单元(如每个LUT、每个触发器)应该放在FPGA芯片内部的哪个具体物理位置上。一个好的布局是实现高性能的关键。

- 布线(Routing):连接信号路径,优化延迟。使用FPGA内部的布线资源(像电线一样),将已经布局好的各个逻辑单元根据网表的连接关系连接起来。

- 运行多次策略:工具会尝试不同优化选项。

- 工具/方法:Vivado Implementation、Quartus Fitter。

- 注意:这一步耗时长(分钟到小时),取决于设计规模。输出包括时序报告、功耗估计。

- 类比:这是“现场施工”阶段。

- 布局:决定哪个房间模块放在哪一层、哪个位置。

- 布线:开始铺设电线、水管、网线,把所有房间连接起来,形成一个完整的系统。

6. 时序分析与优化(Timing Analysis and Optimization)

- 目的:确保设计在目标时钟下稳定运行。

- 具体步骤:

- 静态时序分析(STA):检查建立/保持时间、最大路径延迟。

- 优化:调整约束、添加流水线、Floorplanning(手动布局)。

- 功耗分析:使用工具估算静态/动态功耗。

- 工具/方法:Vivado Timing Analyzer、TimeQuest。

- 注意:时序是 FPGA 设计的痛点,目标是零违规。

- 类比:这是“工程验收”阶段。验收团队(STA)会检查大楼的每一个细节,比如水管压力是否达标(信号延迟是否满足要求),电路是否安全等。

7. 比特流生成与下载(Bitstream Generation and Download)

- 目的:生成可加载到 FPGA 的配置文件。

- 具体步骤:

- 生成比特流(Bitstream):二进制文件,包含配置数据。

- 下载到硬件:使用 JTAG、USB 或 SD 卡加载到 FPGA 开发板。

- 工具/方法:Vivado Programmer、Quartus Programmer;硬件如 Digilent 板或自定义 PCB。

- 注意:比特流大小取决于设计复杂度,确保加密(如果涉及 IP 保护)。

- 类比:生成最终的“大楼启用手册”,里面包含了所有开关、阀门、电路的最终配置信息。

8. 硬件测试与调试(Hardware Testing and Debugging)

- 目的:在实际硬件上验证功能和性能。

- 具体步骤:

- 上板测试:使用示波器、逻辑分析仪检查信号。

- 调试工具:Integrated Logic Analyzer (ILA) 或 SignalTap,捕获内部信号。

- 系统集成:与外部设备(如 CPU、传感器)联调。

- 如果问题,返回前述阶段迭代。

- 工具/方法:ChipScope (Xilinx)、SignalTap (Intel);软件如 Python 脚本自动化测试。

- 注意:硬件 bug 可能源于仿真未覆盖的场景,如噪声或电源问题。

- 类比:大楼竣工,正式通电通水!进入大楼,打开电灯、使用电梯,看看一切是否正常工作。如果发现某个开关有问题,就拿出万用表(ILA)来测量电路,找出问题所在。

9. 发布与维护(Deployment and Maintenance)

- 目的:最终产品化。

- 具体步骤:

- 固化配置:使用 PROM 或 Flash 存储比特流,实现上电自动加载。

- 文档与版本控制:记录设计、测试结果。

- 维护:根据反馈更新设计,支持部分重配置(Partial Reconfiguration)。

- 注意:对于生产级应用,考虑 EMC 测试、可靠性分析。

总体注意事项

- 常见挑战:资源不足、时序关闭、调试难度。优化技巧包括模块复用、时钟域管理。